### High-speed optical interconnects for intra- and inter-DC applications

Dr. Stelios PITRIS Aristotle University of Thessaloniki (AUTH), Greece

virtual conference session: Data Center Interconnects – Towards Mass Manufacturing

online / October 6th 2020 / 4 - 7pm

## **High-speed optical interconnects for intra- and inter-DC applications**

### **Stelios Pitris**

Department of Informatics, Center for Interdisciplinary Research & Innovation, Aristotle University of Thessaloniki (AUTH), Thessaloniki, Greece

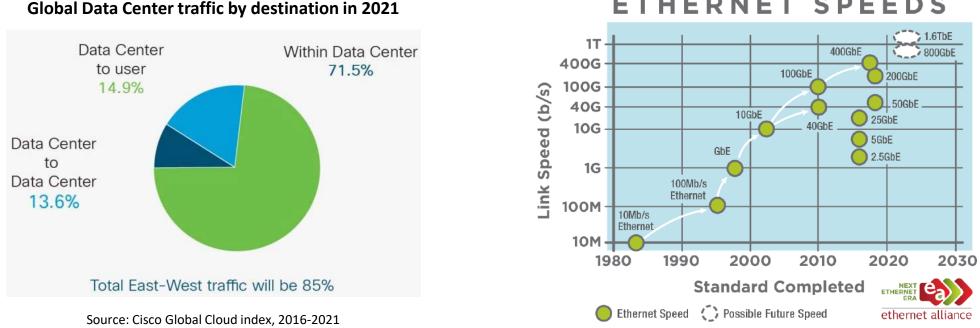

# Motivation for high-speed Transceivers for DC operation

#### HE RNET SPEEDS

### **Emerging DC Transceiver requirements**

- High line-rate

- WDM-functionality

- CMOS-compatibility

- Tight co-packaging with **CMOS** electronics

- Ideally sub-V driving voltage

WinPhoS

# Our work in DC transceivers & interconnect technology

vorget: On-board interconnects for multi-socket computing

Mass-manufacturing of intra- & inter-DC transceivers High-speed plasmonic transceivers for intra- & inter-DC

Photonics Days 2020 Berlin Brandenburg

Aristotle University of Thessaloniki

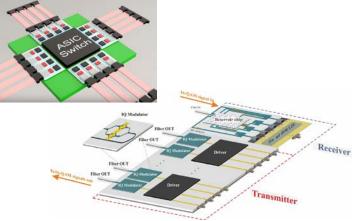

# **ICT-STREAMS:** On-board interconnects for multi-socket boards

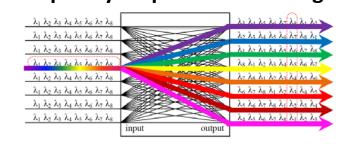

Strictly non-blocking all-to-all connectivity  $\checkmark$

- ✓ Suitable for multi-/broadcasting

- $\checkmark$  High number of ports (up to 32)

- High bandwidth optical links

Aristotle University of Thessaloniki

Photonics Days 2020 Berlin Brandenburg

- BW-independent low-latency links

- ✓ Passive  $\lambda$ -routing

- ✓ Relaxed assembly requirements (VS chip-scale)

- ✓ Low-loss interconnection via O-band polymer WGs

saloniki

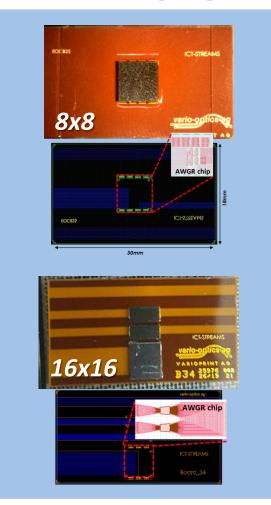

# Si-photonic cyclic passive router evolution within ICT-STREAMS

Aristotle University of Thessaloniki

#### WDM Cyclic AWGR Router Cyclic-frequency all-passive wavelength routing

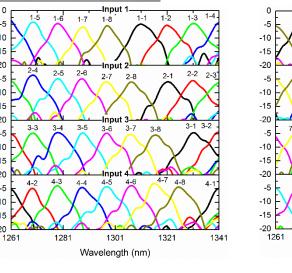

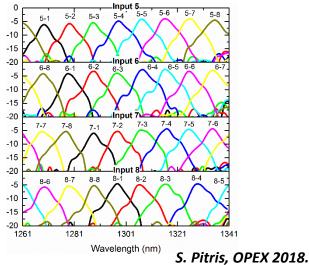

### Si cyclic 8×8 O-band CWDM AWGR

270µm 700µm

> -15 -20

-20

-20

WinPhoS

sion (dBm) -10 -15

- 10 nm (1.77 THz) channel spacing (1260, 1270,..., 1330 nm)

- Cyclic operation validated

ΈΛΕΚ

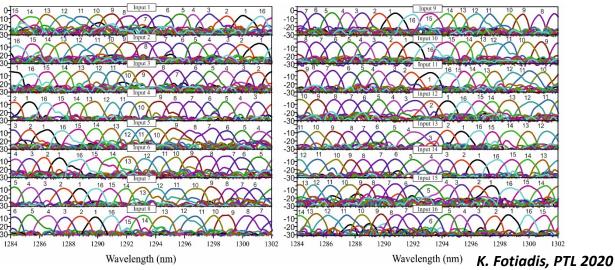

### Si cyclic 16×16 O-band AWGR

- 1.13 nm (200 GHz) channel spacing (1283,9,..., 1300,9 nm)

- Cyclic operation validated

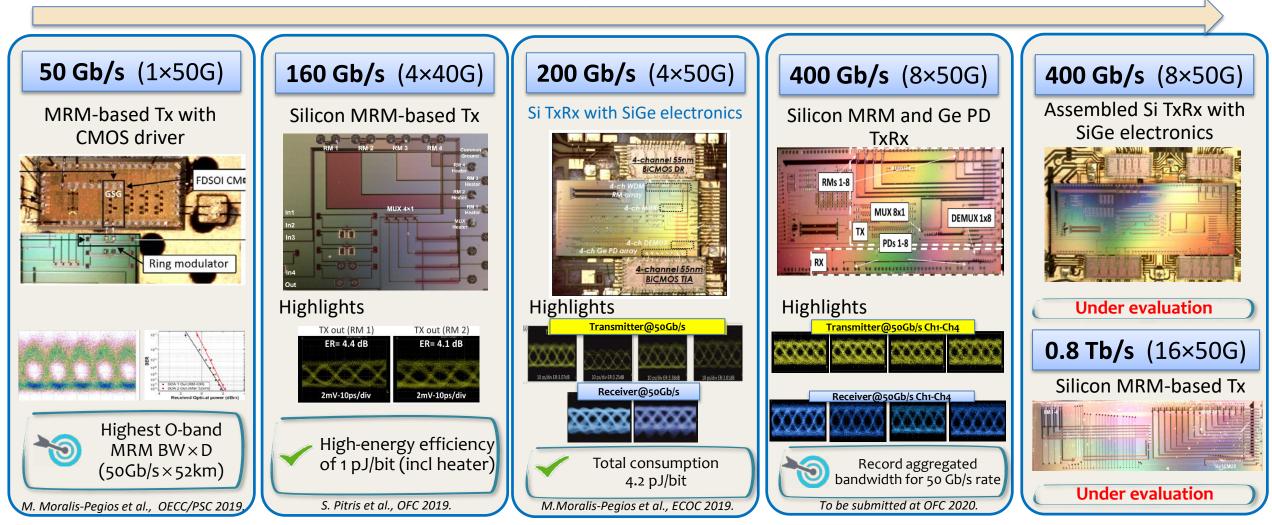

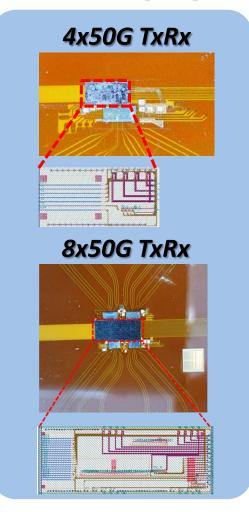

# Si-photonic transceiver assembly evolution within ICT-STREAMS

From 50 Gb/s towards 800 Gb/s

Aristotle University of Thessaloniki

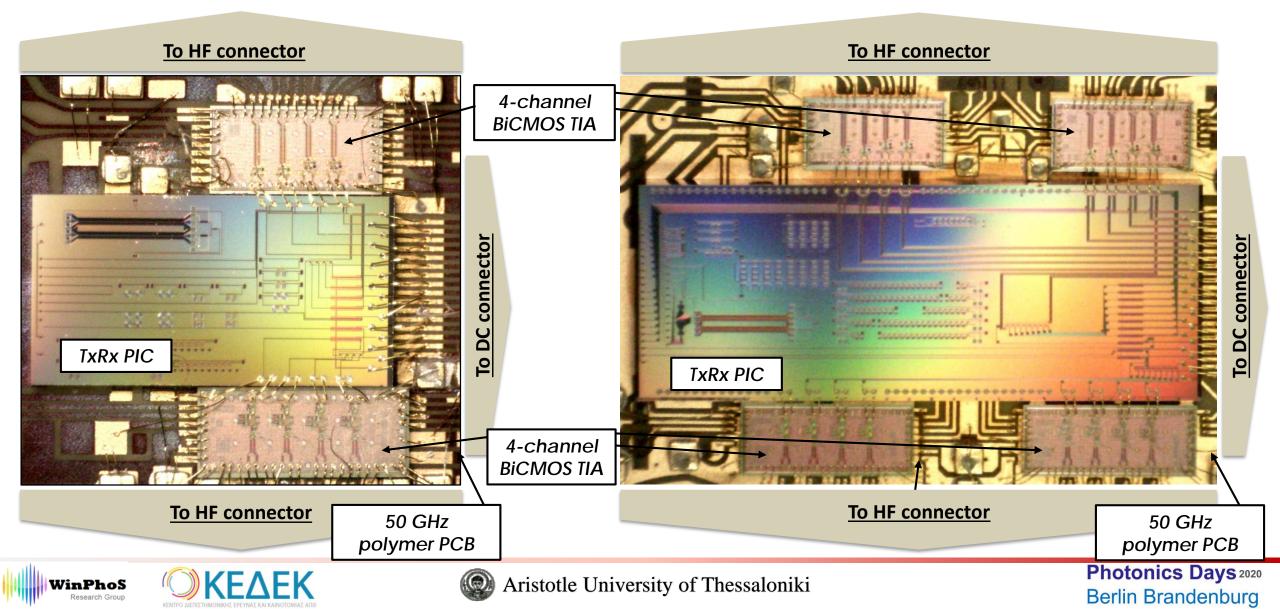

### Transceiver wire-bonded assemblies on PCB with 50 GHz DR/TIA electronics

### WDM 4-channel TxRx assembly

#### WDM 8-channel TxRx assembly

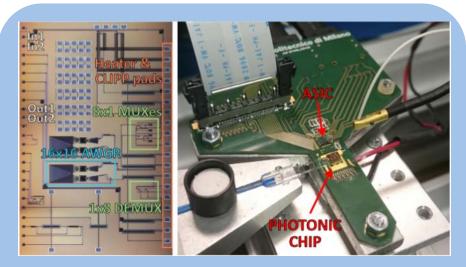

# Currently under evaluation & further development

#### Board-pluggable Si-AWGR Board-pluggable TxRxs routers on polymer with EICs on polymer

#### 2-socket demonstrator with thermal drift compensation

#### F. Zanetto, JLT 2020.

#### Photonic chip

- TxRx circuitry

- *MUX circuitry*

- Routing circuitry

#### Feedback & control

- Front-end ASIC

- FPGA control

- Hosting board

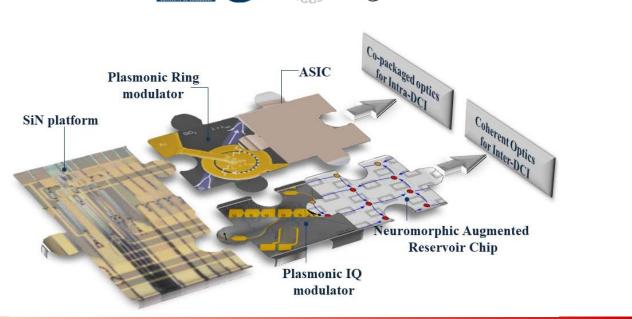

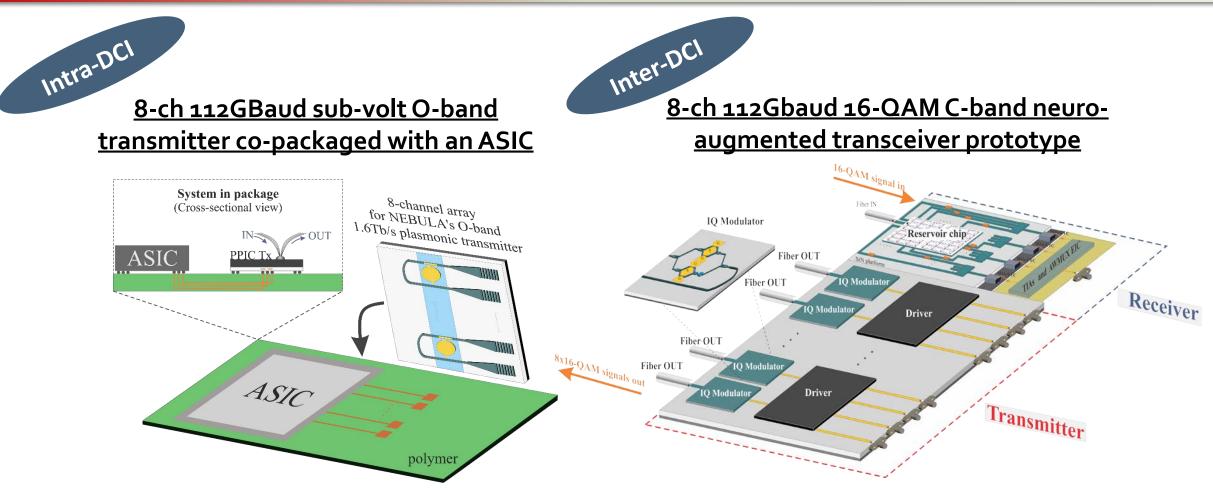

# **NEBULA:** neuro-augmented TxRxs for intra- and inter-DC apps

**NEBULA** aims to deliver a powerful neuro-augmented 112Gbaud CMOS plasmonic transceiver platform for Intra- and Inter-DCI applications

**Coordinator: AUTH**

### **Key Technologies:**

- 112GBaud plasmonic modulators on SiN based on ferroelectric BTO

- Loss-less thermal stabilization circuit

- Neuro-augmented all-optical DSP on the Rx

- 112GBaud BiCMOS ultra-fast electronics

F

imec

//Lumiphase

# NEBULA targeted transceiver prototype portfolio

- ✓ Tx: 112Gbaud PAM4 disk/MZIR modulators ✓ Tx: 112Gbaud PAM4 IQ modulators

- ✓ Co-packaged with data generating ASIC

✓ Rx: Reservoir-assisted DSP-free

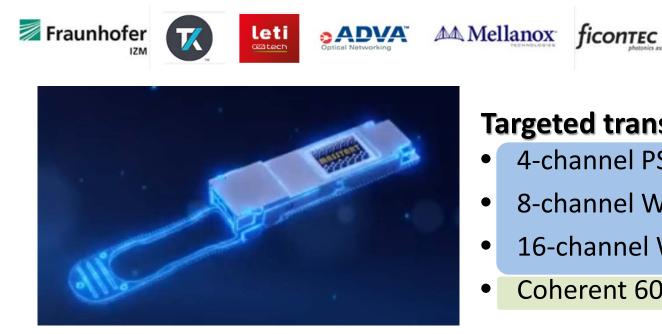

## MASSTART: mass manufacturing of intra- & inter-DC transceivers

**MASSTART** targets to deliver a pioneering assembly and characterization framework for highspeed photonic transceivers

### **Targeted transceiver prototypes:**

• 4-channel PSM4 400G (56G PAM4) transceiver

rteem

- 8-channel WDM 800G (56G PAM4) transceiver

- 16-channel WDM 1.6T (56G PAM4) transceiver

- Coherent 600G 64QAM-DP transceiver

O-band for intra-DC C-band for inter-DC

dust photonics

# AUTH contribution: automated testing platform

<u>Automated die tester</u> **Automation for various** ARISTOTLE ficontec UNIVERSITY OF probe setup by: characterization tasks by: THESSALONIKI Voltage Multimeter Ficontec source **OSAs/powerme** auto die **Tunable laser** ter tostor **PNA/VNA PNA/VNA** Pattern gen **BERT/data Rx** Automatic optical alignment Control plane: LabView connectivity

#### **Automated tasks**

- > Task #1: Passive characterization (frequency sweeping) & DC

- Task #2: Electrical characterization

- > Task #3: E/O characterization

- > Task #4: Data generation, transmission, reception & analysis

**Probe capabilities**

Dc probing

**RF** probing

WinPhoS 🏾

**Optical probing**

## Work sum up

□ ICT-STREAMS: On-board interconnects for multi-socket server boards

- Passive routing components

- Transceiver PICs and assemblies: from 50G to 800G NRZ

□ NEBULA: neuro-augmented TxRxs for intra- and inter-DC apps

- Targeted intra-DC plasmonic transmitter co-packaged with ASIC

- Targeted inter-DC plasmonic transceiver with neuro-augmented DSP-free reception

- □ MASSTART: mass manufacturing of intra- & inter-DC transceivers

- Development of an automated die testing platform for high-speed transceiver components

### Thank you

### **Funding & AUTH teams**

H2020-MASSTART (ongoing)

H2020-NEBULA (ongoing)

H2020-ICT-STREAMS (ended Nov 2019) Dr. S. Pitris, T. Chrysostomidis Dr. A. Totovic Dr. D. Tsiokos Profs. K. Vyrsokinos & N. Pleros

Dr. S. Pitris

- G. Mourgias

- T. Chrysostomidis

- G. Roumbos

- D. Chatzitheocharis

- N. Terzenidis, E. Chatzianagnostou Profs. K. Vyrsokinos & N. Pleros

Dr. T. Alexoudi Dr. S. Pitris Dr. M. Moralis Pegios Dr. G. T. Kanellos Profs. K. Vyrsokinos & N. Pleros

WinPhoS <u>http://winphos.web.auth.gr</u>

SCHOOL OF INFORMATICS

SCHOOL OF ELECTRICAL & COMPUTER ENGINEERING

### Acknowledgement

Co-funded by the Horizon 2020

Framework Programme of the European Union

MASSTART project is co-funded by the Horizon 2020 Framework Programme of the European Union with Grant Agreement Nr. 825109. https://cordis.europa.eu/project/rcn/219912/factsheet/en

MASSTART project is an initiative of the **Photonics Public Private Partnership** <u>www.photonics21.org</u>

#Photonics@Photonics21@PhotonicsEU#H2020

**Disclaimer:** The information, documentation and figures available in this deliverable are written by the MASSTART Consortium Partners under co-funding by Horizon 2020 Framework Programme of the European Union (Grant agreement ID: 825109) and do not necessarily reflect the view of the European Commission. The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The reader uses the information at his/her sole risk and liability.

Copyright © 2020 the MASSTART Consortium. All rights reserved. This document may not be copied, reproduced or modified in whole or in part for any purpose without written permission from the MASSTART Consortium. In addition to such written permission to copy, reproduce or modify this document in whole or part, an acknowledgement of the authors of the document and all applicable portions of the copyright notice must be clearly referenced.

MASSTART Consortium

Data Center Interconnects - Towards Mass Manufacturing, 6th October 2020