#### **Develop your custom Photonic Integrated Circuit for Data Centers**

Dr. Katarzyna ŁAWNICZUK VP, Bright Photonics BV, Netherlands

virtual conference session: Data Center Interconnects – Towards Mass Manufacturing

online / October 6th 2020 / 4 – 7pm

## Develop your custom Photonic Integrated Circuit for Data Centers

#### Technology selection and design & validation

Katarzyna Ławniczuk k.lawniczuk@brightphotonics.eu

Photonics Days 2020 – Berlin Brandenburg 6 October 2020

www.brightphotonics.eu

BRIGHT Photonics B.V. (C)

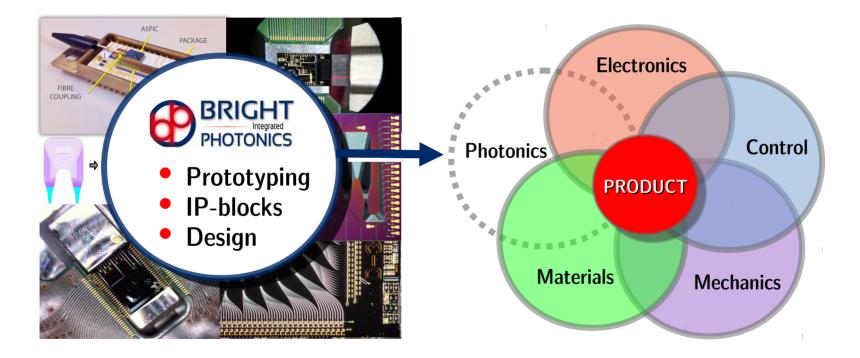

# About BRIGHT Photonics:

#### Empowering products with photonic engineering

### **About BRIGHT Photonics:**

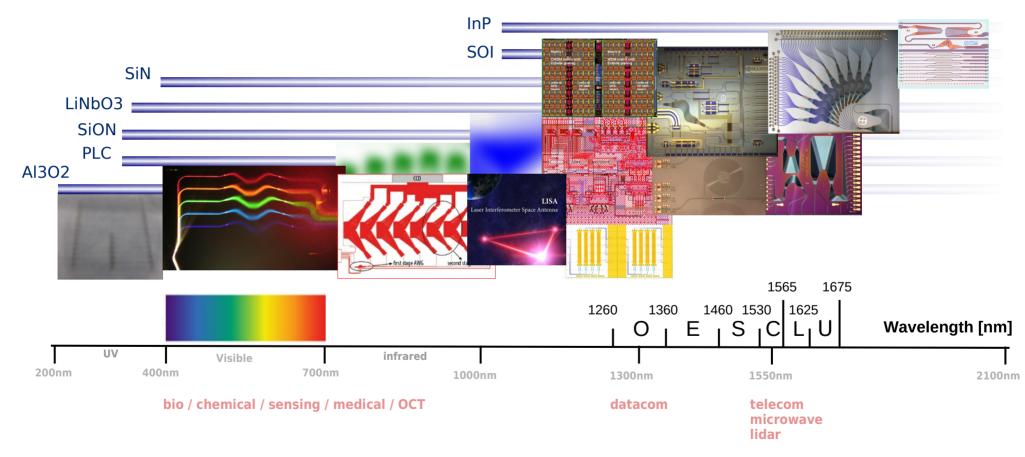

#### Design across wavelengths from UV to IR

3

# About BRIGHT Photonics:

#### Design across wavelengths from UV to IR

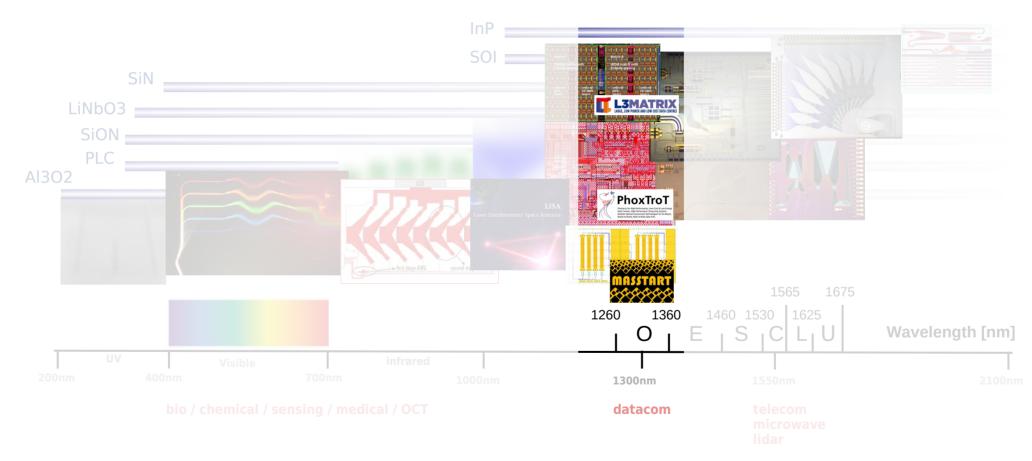

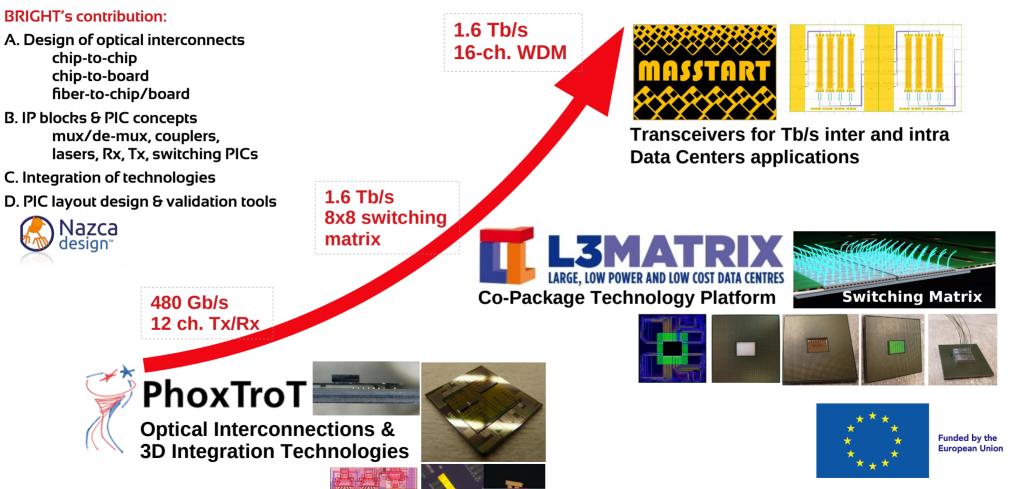

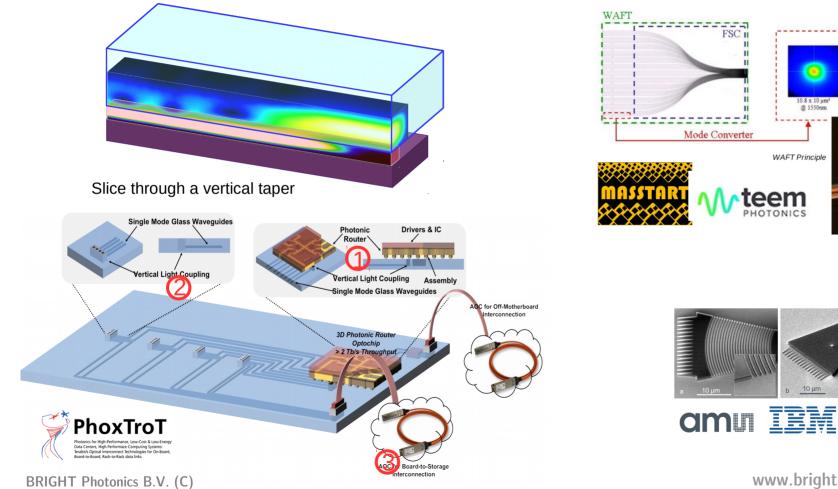

#### **Development beyond 400G in EU projects**

BRIGHT Photonics B.V. (C)

5

4.1 x 3.1 μm<sup>2</sup> @ 1550nm

Tapered

waveguide

10.8 x 10 µm

@ 1550nm

10 µm

Confined

waveguide

#### A. Optical interconnects

www.brightphotonics.eu

6

#### **B. IP-blocks and PIC concepts**

• Commercial MUX and DeMUX components

• Lasers (O-band, C-band)

• Spot-size converters

• Polarization handling devices

#### **B. IP-blocks and PIC concepts**

#### • Commercial MUX and DeMUX components

- Lasers (O-band, C-band)

- Spot-size converters

• Polarization handling devices

|                     |                               |               | أستنبط أستنبطة          | والمنصور المستبيدات           |

|---------------------|-------------------------------|---------------|-------------------------|-------------------------------|

| NEL 1938 1833 1938  |                               |               | 🕮 🖃 🏙 🕮                 |                               |

|                     |                               |               |                         |                               |

| Matrix I            |                               | Matrix II     |                         | 100 100                       |

|                     |                               |               |                         |                               |

| CWDM m              | atrix with                    | 🗖 🗧 WDM m     | atrix with              |                               |

| Echelle g           | rating                        | Echelle       | grating                 |                               |

| ANDA ANDA ANDA ANDA |                               |               |                         |                               |

|                     |                               |               |                         |                               |

|                     |                               | AMZI          |                         |                               |

| in the switch       |                               | tests units w |                         | ts-w/<br>DBR<br>assives tests |

| DFB                 | FP-DBR                        | DFB           |                         | DBR                           |

| lasers              | lasers                        | lasers        | lase lase               | ers 🚺 🦉                       |

|                     |                               |               |                         |                               |

|                     |                               |               |                         |                               |

|                     |                               |               |                         |                               |

|                     | a a salat salat salat salat s |               | alah ini ini adasi saba | select select                 |

|                     |                               |               |                         |                               |

|                     |                               |               |                         |                               |

L3Matrix: switching matrix

8

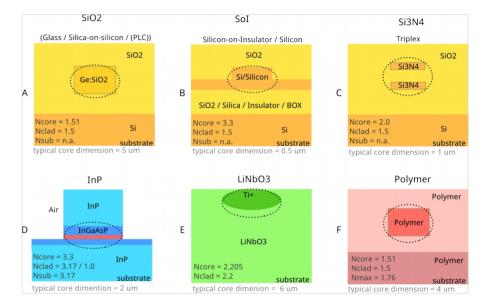

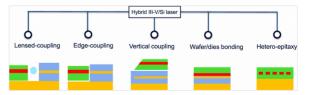

# C. Integration technologies: combining (low-loss) passives and actives

#### → monolithic vs. hybrid integration

Variety of material platforms

9

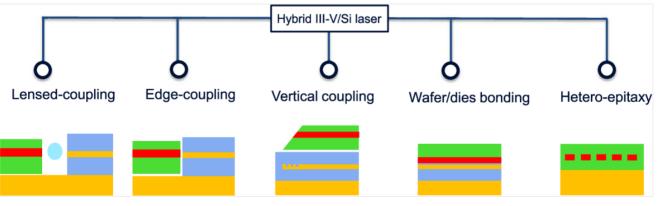

# C. Integration technologies: combining (low-loss) passives and actives

- → monolithic vs. hybrid integration

- → hybrid III-V/Si laser integration

G. de Valicourt et al., JLT, 36 (2) 2018.

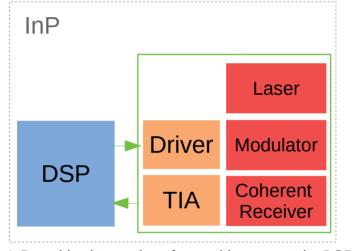

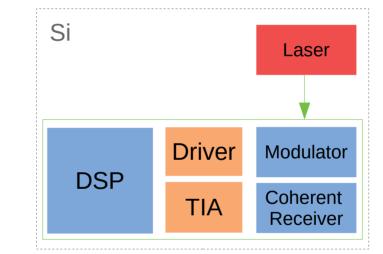

#### C. Integration technologies: Transceivers always combine InP and Si

CMOS

SiGe

InP

InP enables integration of everything except the DSP

Si enables integration of all electronic and photonic components except the laser

#### C. Integration technologies: comparison

|                            |                         | InP (generic<br>integration)                              | SiP with<br>external lasers           | Heterogeneous integration (SOI)    | Epitaxial<br>growth on Si   |

|----------------------------|-------------------------|-----------------------------------------------------------|---------------------------------------|------------------------------------|-----------------------------|

| Technical                  | Optical loss            |                                                           | 0.1 dB LETI (rib)                     |                                    |                             |

|                            | Active/lasers coupling  | 0.1 dB butt-join                                          | 2-8 dB chip-to-chip                   | 0.5 dB taper loss                  | 0.1 dB butt-join            |

|                            | Photodiodes             |                                                           |                                       |                                    |                             |

|                            | Mux/DeMUX               |                                                           |                                       |                                    |                             |

|                            | Polarization Control    |                                                           |                                       |                                    |                             |

|                            | Electronics integration |                                                           |                                       |                                    |                             |

| Production                 | III-V substrate         | 1                                                         | ~                                     | 1                                  | -                           |

|                            | III-V growth            | 1                                                         | ~                                     | 1                                  | 1                           |

|                            | SOI/Si substrate        | -                                                         | 1                                     | 1                                  | 1                           |

|                            | Footprint               | High index contrast in 1D                                 | High index contrast in 2D             | High index contrast in 2D          | High index contrast in 2D   |

|                            | Yield                   |                                                           | CMOS level                            |                                    |                             |

| Economic                   | Substrate cost (\$/cm²) | 4.5                                                       | 0.2                                   | 1.5                                | 0.2                         |

|                            | Assembly costs          | Fiber coupling                                            | Laser coupling                        | III-V bonding                      | Fiber coupling              |

|                            | Testing                 | Wafer level                                               | Lasers, SiP                           | Wafer level                        | Wafer level                 |

|                            | Wafer size/scaling up   | 100 mm                                                    |                                       | 300 mm                             |                             |

| Foundries / Product owners |                         | Smart Photonics,<br>Fraunhofer HHI /<br>Infinera, Finisar | VTT, LETI, imec /<br>Luxtera, Rockley | LETI, imec, TU/e - IMOS<br>/ Intel | Under research<br>AIM, imec |

#### C. Integration technologies: comparison

|                            |                         | InP (generic<br>integration)                              | SiP with<br>external lasers           | Heterogeneous integration (SOI)    | Epitaxial<br>growth on Si   |

|----------------------------|-------------------------|-----------------------------------------------------------|---------------------------------------|------------------------------------|-----------------------------|

| Technical                  | Optical loss            |                                                           | 0.1 dB LETI (rib)                     |                                    |                             |

|                            | Active/lasers coupling  | 0.1 dB butt-join                                          | 2-8 dB chip-to-chip                   | 0.5 dB taper loss                  | 0.1 dB butt-join            |

|                            | Photodiodes             |                                                           |                                       |                                    |                             |

|                            | Mux/DeMUX               |                                                           |                                       |                                    |                             |

|                            | Polarization Cont       |                                                           |                                       |                                    |                             |

|                            | Electronics integr      | Applicat                                                  | ion / Spec                            |                                    |                             |

| Production                 | III-V substrate         | Volume                                                    | ion / Spec                            | ~                                  | -                           |

|                            | III-V growth            |                                                           |                                       | ~                                  | 1                           |

|                            | SOI/Si substrate        | Yield                                                     |                                       | 1                                  | 1                           |

|                            | Footprint               | Cost                                                      |                                       | th index contrast in 2D            | High index contrast in 2D   |

|                            | Yield                   |                                                           |                                       | CMOS level                         |                             |

| Economic                   | Substrate cost (\$/cm2) | 4.5                                                       | 0.2                                   | 1.5                                | 0.2                         |

|                            | Assembly costs          | Fiber coupling                                            | Laser coupling                        | III-V bonding                      | Fiber coupling              |

|                            | Testing                 | Wafer level                                               | Lasers, SiP                           | Wafer level                        | Wafer level                 |

|                            | Wafer size/scaling up   | 100 mm                                                    |                                       | 300 mm                             |                             |

| Foundries / Product owners |                         | Smart Photonics,<br>Fraunhofer HHI /<br>Infinera, Finisar | VTT, LETI, imec /<br>Luxtera, Rockley | LETI, imec, TU/e - IMOS<br>/ Intel | Under research<br>AIM, imec |

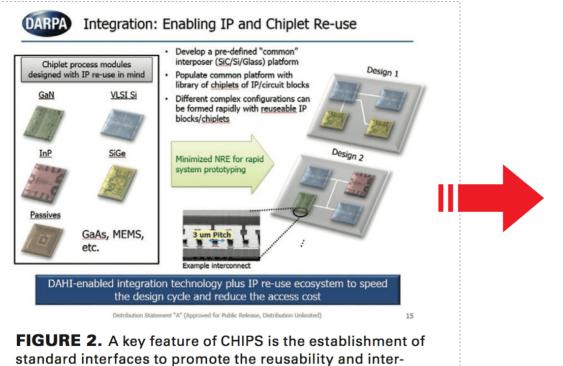

### C. Integration technologies: Moving towards complex modular systems

changeability of modular circuit functional blocks or chiplets.

#### Beyond 50000G?

50 GHz bandwidth x 2 symbols per period x 4 bits per symbol (16QAM) x 8 lanes x 8 wavelengths x 2 polarizations

= 51.2 Tb/s

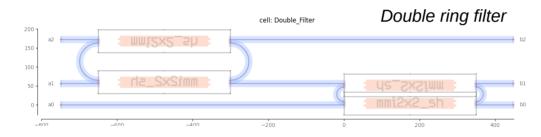

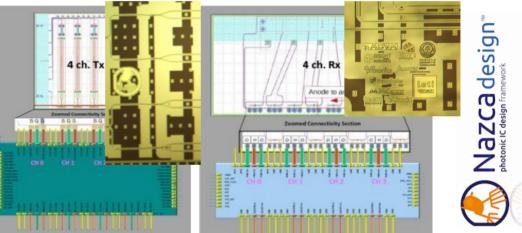

# D. Design and validation with Nazca-Design

- Combine multiple technologies Hybrid design

- ➔ Si-Photonics, III-V, Glass

- ➔ Develop PDK, define and separate technology layers: layers mapping

- Exchange IP Building Blocks IP protection

- ➔ Combine files and create libraries with GDS BBs, cells mapping

- → IP BBs handling, work with GDSII standard

- ➔ Facilitated GDSII files scaling and proper accuracy

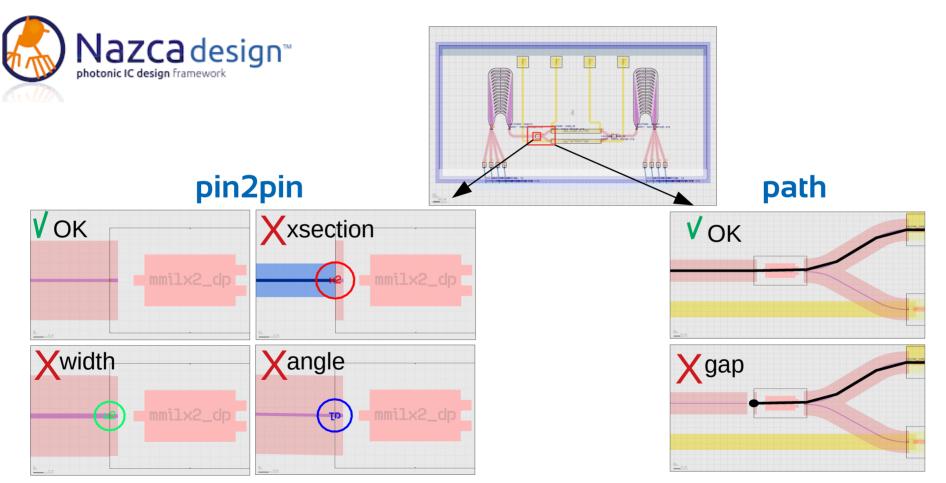

- ✓ Solve complex routing and DRC

- Create interconnects and routing for circuits connectivity with error-free implementation & DRC on connectivity

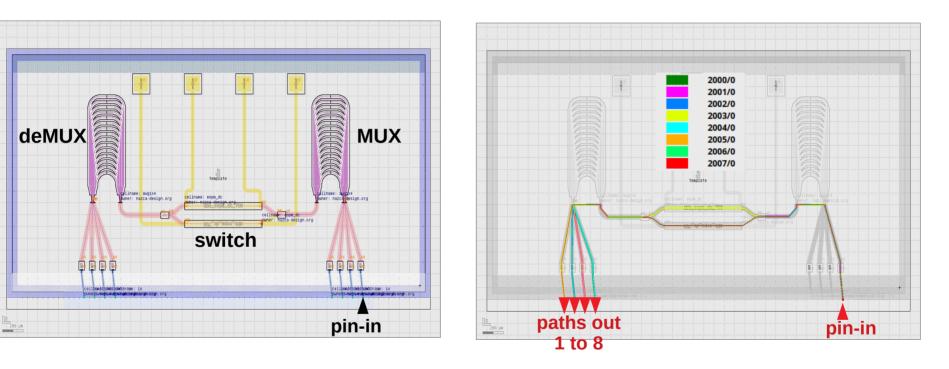

- ➔ Path tracing for circuit integrity

- Facilitate new generation of assembly, coupling and packaging approaches

- ➔ Create packaging rules, packaging templates,

- ➔ Import fiducials, drivers, tias

# import PDK

# import IP BBs

# import Packages

import nazca

import leti

import teem

import izm

import ficontec

import bright

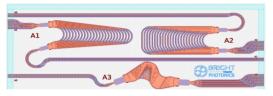

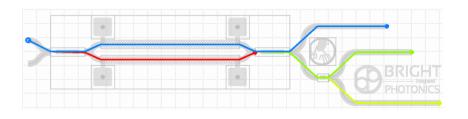

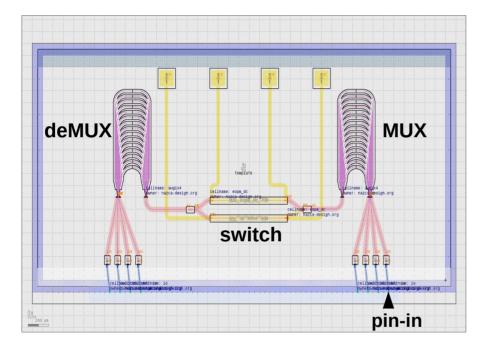

#### D. Design and validation in GDS

#### D. Design and validation in GDS: path tracing

www.brightphotonics.eu

BRIGHT Integrated PHOTONICS

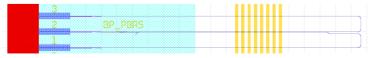

# D. Design and validation in GDS: connection DRC

#### **18** BRIGHT Photonics B.V. (C)

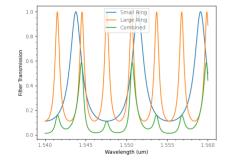

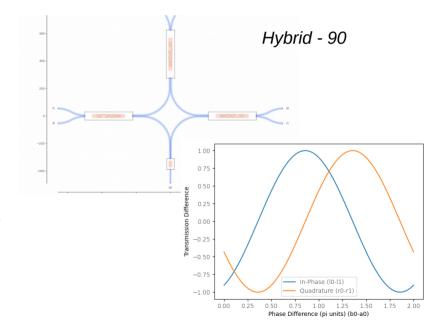

### D. Design and validation in GDS: circuit simulation and verification at GDS level

#### Examples:

- Investigation of filtering characteristics

- Transmission simulation of a circuit

- Integration of Material models in PDK and components S-matrices

### D. Design and validation with Nazca-Design

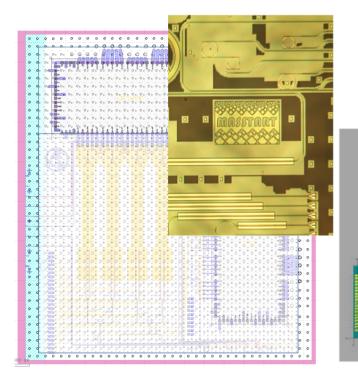

# Tape-out of MASSTART inter- and intra- Data Center PICs

# Thank you!

#### Contact: info@BrightPhotonics.eu

Supply chain development

PIC concepts & IP blocks

Prototyping & Design

MASSTART team: Marco Passoni Katarzyna Ławniczuk Ronald Broeke

#### Acknowledgement

Co-funded by the Horizon 2020

Framework Programme of the European Union

MASSTART project is co-funded by the Horizon 2020 Framework Programme of the European Union with Grant Agreement Nr. 825109. https://cordis.europa.eu/project/rcn/219912/factsheet/en

MASSTART project is an initiative of the **Photonics Public Private Partnership** <u>www.photonics21.org</u>

#Photonics@Photonics21@PhotonicsEU#H2020

**Disclaimer:** The information, documentation and figures available in this deliverable are written by the MASSTART Consortium Partners under co-funding by Horizon 2020 Framework Programme of the European Union (Grant agreement ID: 825109) and do not necessarily reflect the view of the European Commission. The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The reader uses the information at his/her sole risk and liability.

Copyright © 2020 the MASSTART Consortium. All rights reserved. This document may not be copied, reproduced or modified in whole or in part for any purpose without written permission from the MASSTART Consortium. In addition to such written permission to copy, reproduce or modify this document in whole or part, an acknowledgement of the authors of the document and all applicable portions of the copyright notice must be clearly referenced.

MASSTART Consortium

Data Center Interconnects - Towards Mass Manufacturing, 6th October 2020