## **3D integration for next generation transceiver PICs**

**Bogdan Sirbu**

Fraunhofer Institute for Reliability and Microintegration (IZM), BerlinPhotonics days Berlin Brandenburg 2021

### Data Age - Global datasphere by 2025

163ZB

Amount of data that will be created annually 20% Amount of

life-critical data in datasphere

# 4800/day

Amount of one persons interaction with IoT devices

25%

Amount of created real-time data in datasphere 5.2ZB

Amount of data that subject to **data analysis**  **1.4ZB**

Amount of analysed data touched by AI / cognitive systems 90% Amount of da

Amount of data in datasphere require security

Source: IDC, Seagate

1 zettabyte : 10<sup>21</sup> bytes

Bogdan Sirbu, WLSI

2 Photonics Days Berlin Brandenburg, 05.10.2021 © Fraunhofer IZM

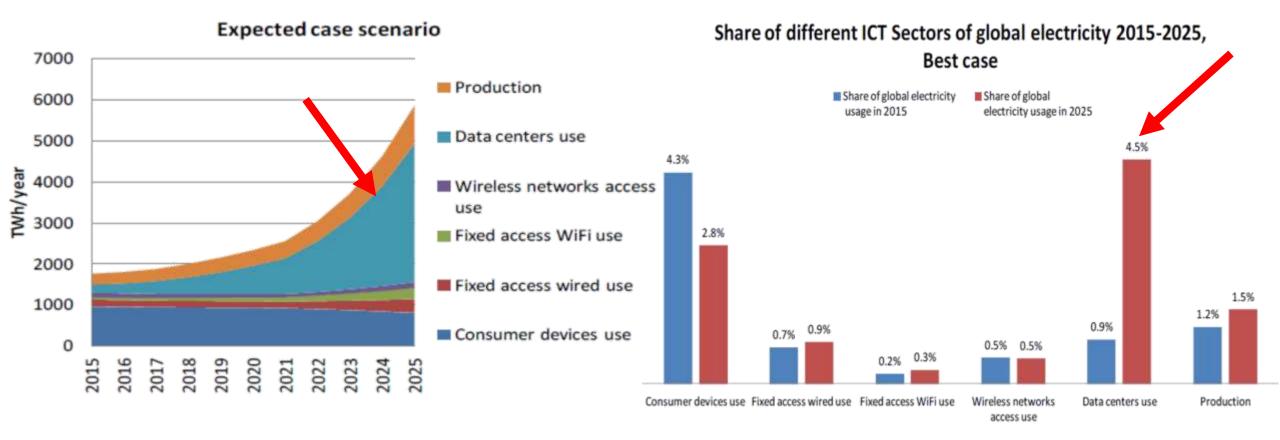

### The Downside

Source: Total consumer power consumption forecast, Dr. Anders S. G. Andrae (Huawei), Nordic Digital Business Summit, October 2017

Bogdan Sirbu, WLSI

© Fraunhofer IZM

PHOTONICS PUBLIC PRIVATE PARTNERSHI

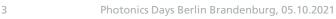

### Silicon Photonics Chip Forecast for DCI

Source: Yole

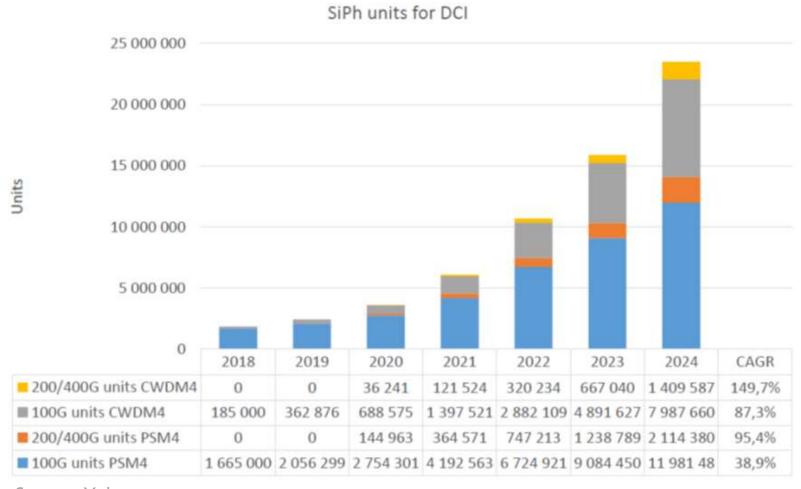

### **Photonics Packaging Key Challenges**

Si microphotonic devices cost

In photonics, packaging & assembly still account for 85% of the total cost (Facebook source)

- High precision placement for fiber **alignment** for SM

- Delicate parts handling

- Different **die attach** technologies for assembly

- Testing

- **Standardization**

- Reliability

- Small and odd shape devices

- High cost

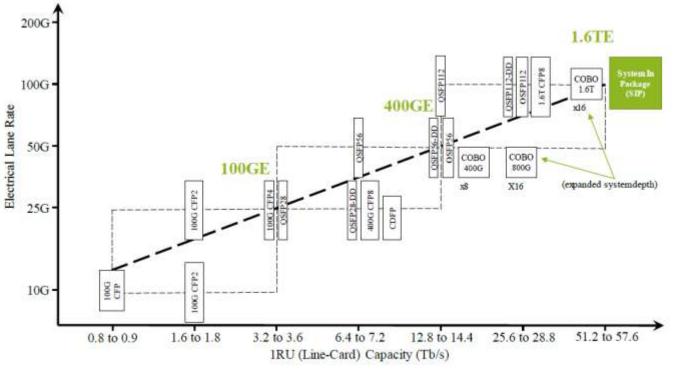

### **Ethernet speed – Historical Data and Forecast**

- Next stop, 800G and 1.6T

- Road >400G includes COBO and co-packaging

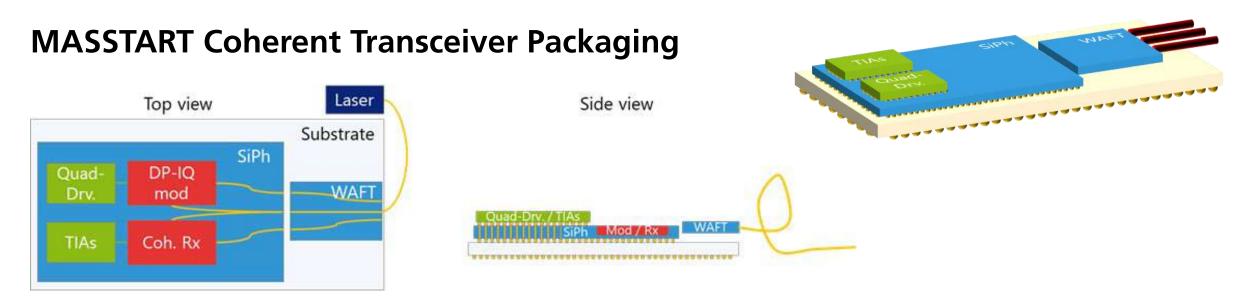

### MASSTART surpasses the cost metric threshold by using enhanced and scalable techniques

- Glass interface based laser/PIC and fiber/PIC coupling approaches, leveraging glass waveguide technology to obtain spot size and pitch converters in order to dramatically increase optical I/O density, while facilitating automated assembly processes,

- **3D** packaging (**TSV**) enabling backside connection of the high speed PIC to a Si carrier,

- A new generation of flip chip bonders with enhanced placement in a complete assembly line compatible with Industry 4.0 which will guarantee an x6 improvement in throughput

- Wafer-level evaluation of assembled circuits with novel tools that will reduce the characterization time by a factor of 10, down to 1 minute per device.

- 4-channel PSM4 module in QSFP-DD format with 400G aggregate bit rate,

- 8-channel WDM module in a QSFP-DD format with 800G aggregate bit rate,

- 16-channel WDM on-board module delivering 1.6Tb/s aggregate line rate,

- A tunable single-wavelength coherent transceiver with 600Gb/s capacity following the DP-64QAM modulation format on 64Gbaud/s line rate.

www.masstart.eu

### **MASSTART – Consortium as a whole**

System providers

#### Photonic Assembly & Testing

Design House & Technology consultancy

#### Technology providers

www.masstart.eu

PHOTONICS FUEL C PRIVATE PARTNERSHIP

Bogdan Sirbu, WLSI

Photonics Days Berlin Brandenburg, 05.10.2021

© Fraunhofer IZM

Fraunhofer

Ø

- ✓ Glass interface based laser/PIC and fiber/PIC coupling approaches

- $\rightarrow$  obtain spot size and pitch converters

- → increase optical I/O density, automated assembly processes

- ✓ 3D packaging using TSV enabling backside connection of the high speed PIC to a Si carrier

- New flip chip bonders with enhanced placement

- $\rightarrow$  improvement in throughput

- Wafer-level evaluation of assembled circuits with novel tools

- $\rightarrow$  reduce characterization time

Bogdan Sirbu, WLSI

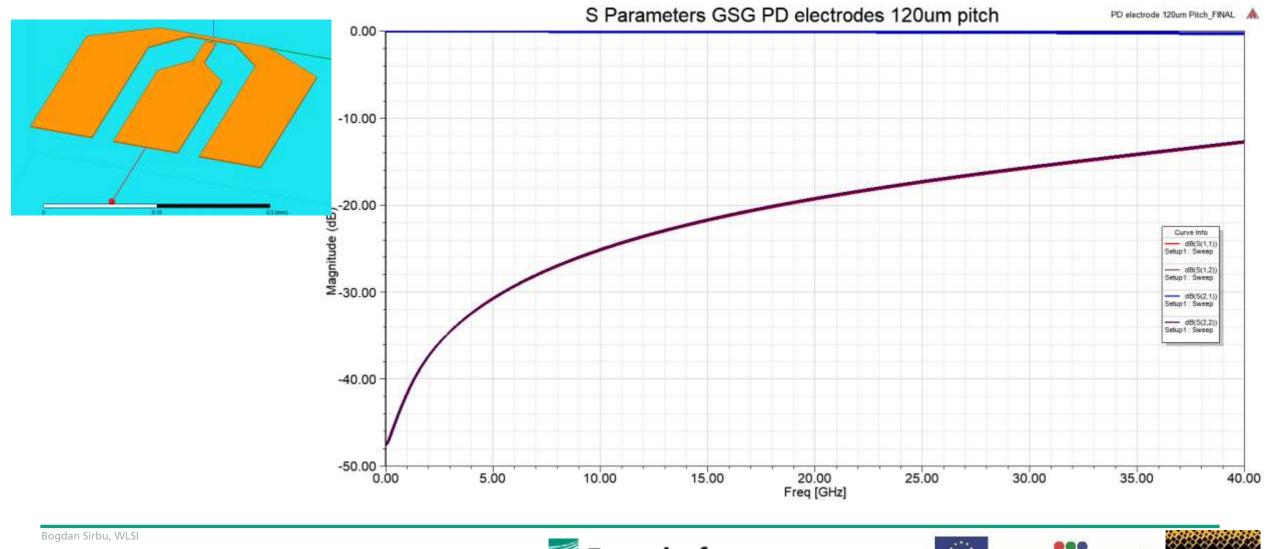

### **MASSTART – 120um pitch PD 50ohm GSG electrodes**

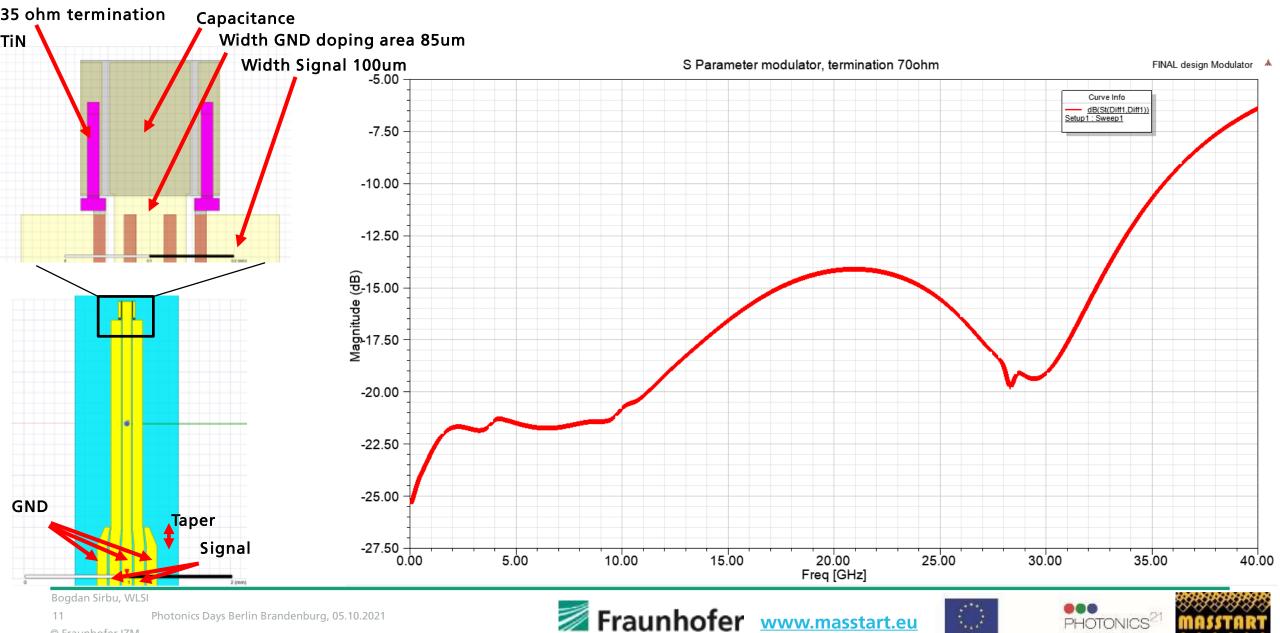

### **Modulators - optimization GSGSG 70ohm termination**

© Fraunhofer IZM

IZM

PHOTONICS FUEL C PRIVATE PARTNERSHIP

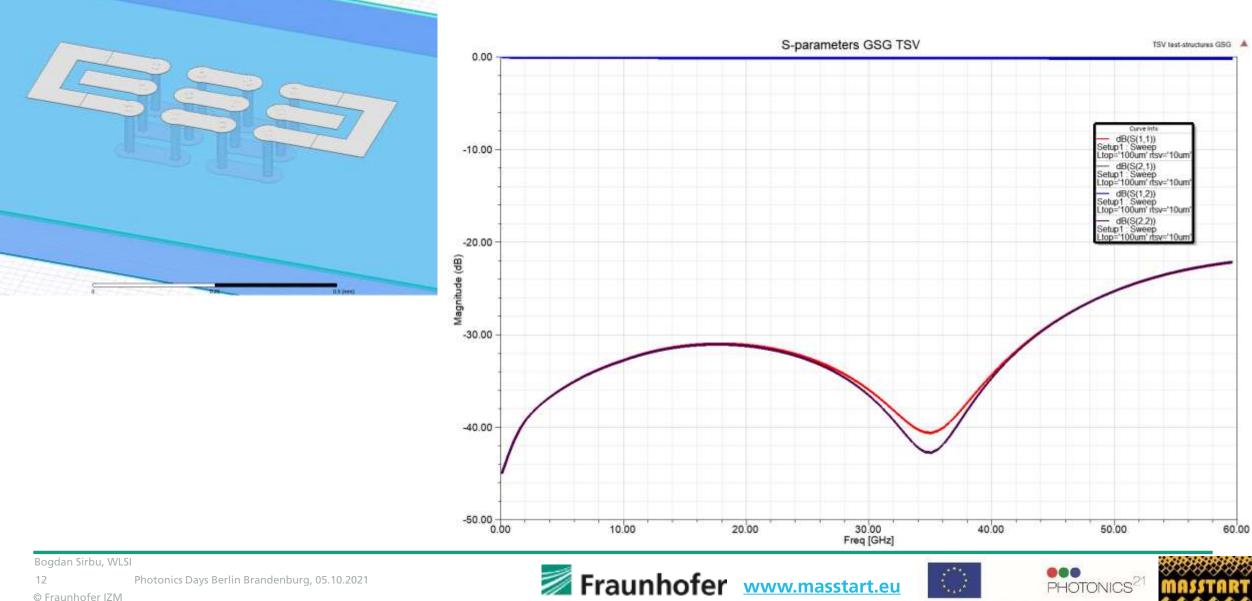

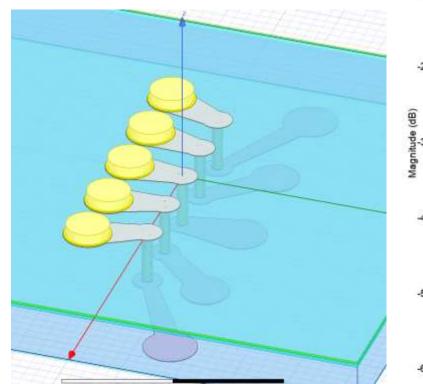

#### **TSV Test-structures GSG**

© Fraunhofer IZM

IZM

PHOTONICS FUBLIC PRIVATE PARTNERSHIP

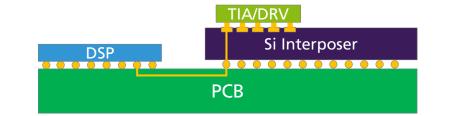

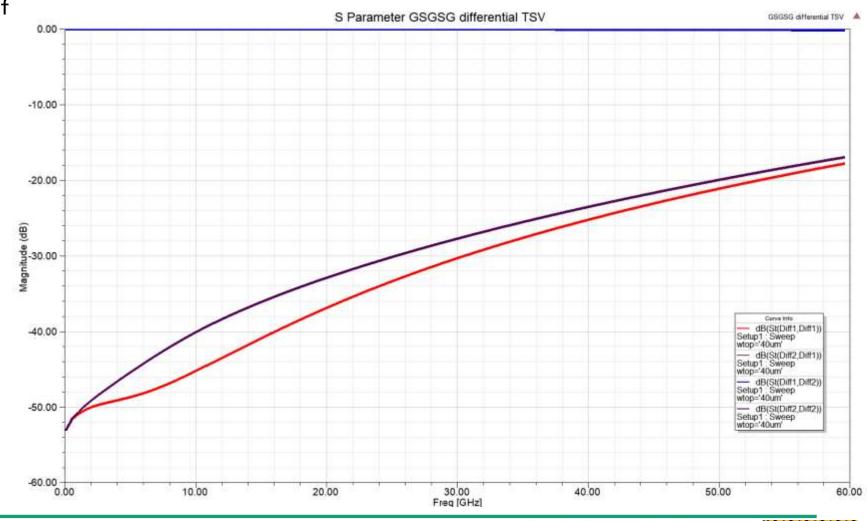

### **GSGSG TSV Application Scenario**

Required to connect:

- Driver/TIA chips assembled on top of the Interposer

- DSP chip assembled on the PCB

Bogdan Sirbu, WLSI13Photonics Days Berlin Brandenburg, 05.10.2021© Fraunhofer IZM

PHOTONICS PUBLIC PRIVATE PARTNERSHI

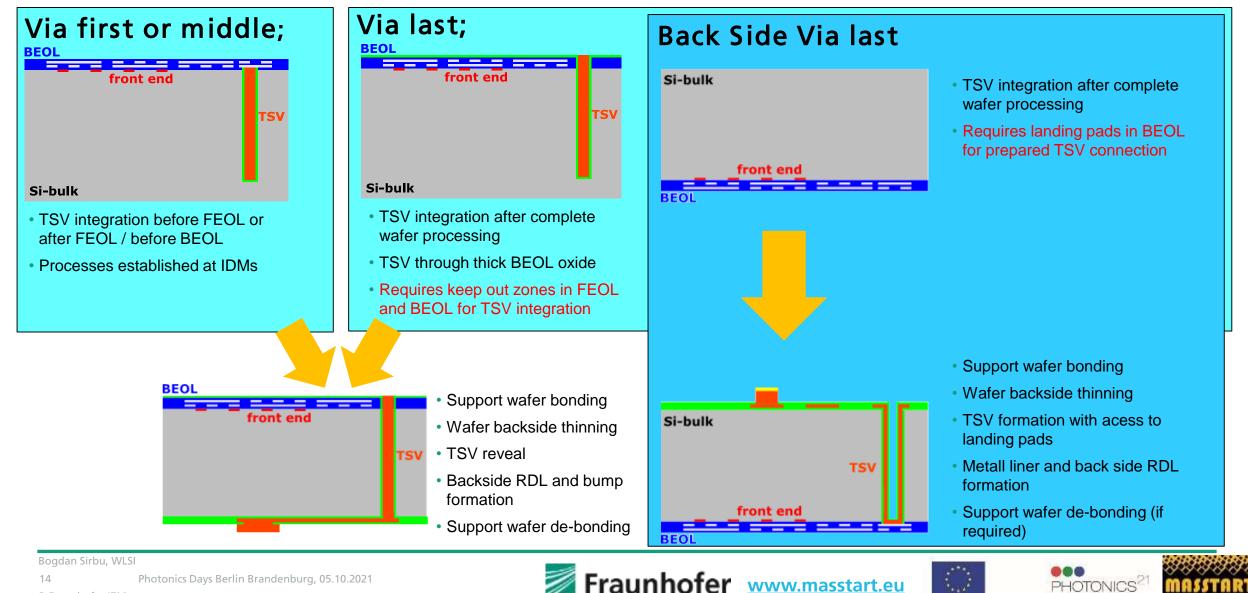

### **TSV Integration Schemes**

PHOTONICS FUBLIC PRIVATE PARTNERSHIT

www.masstart.eu

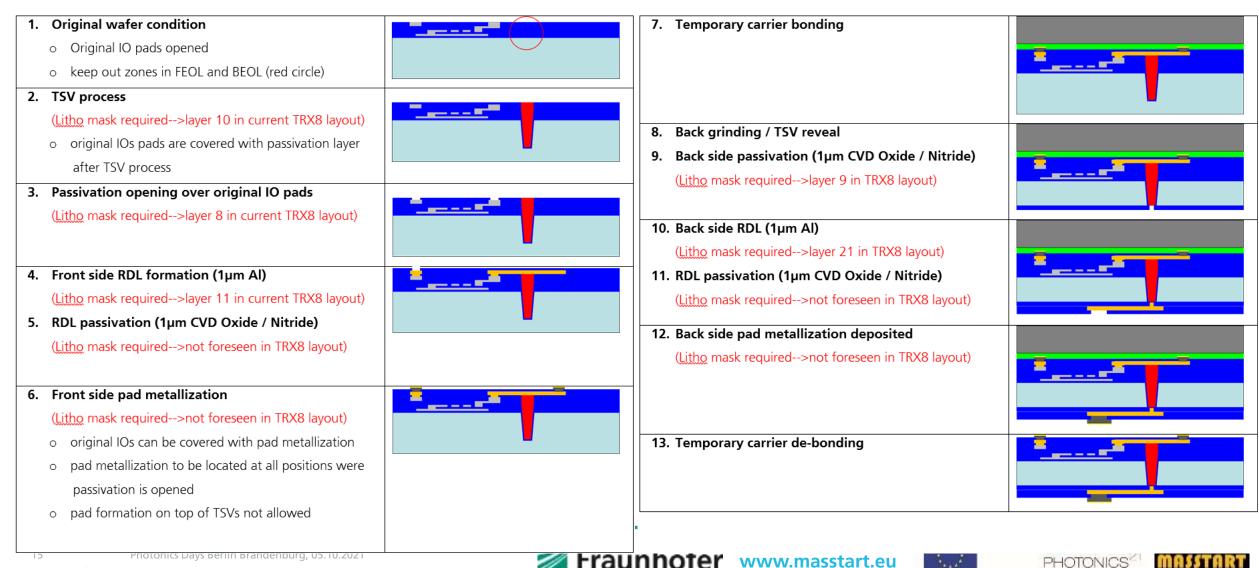

### Front and Back Side Processes for TSV, RDL and IO formation

© Fraunhofer IZM

PHOTONICS PUBLIC PRIVATE PARTNERSHIP

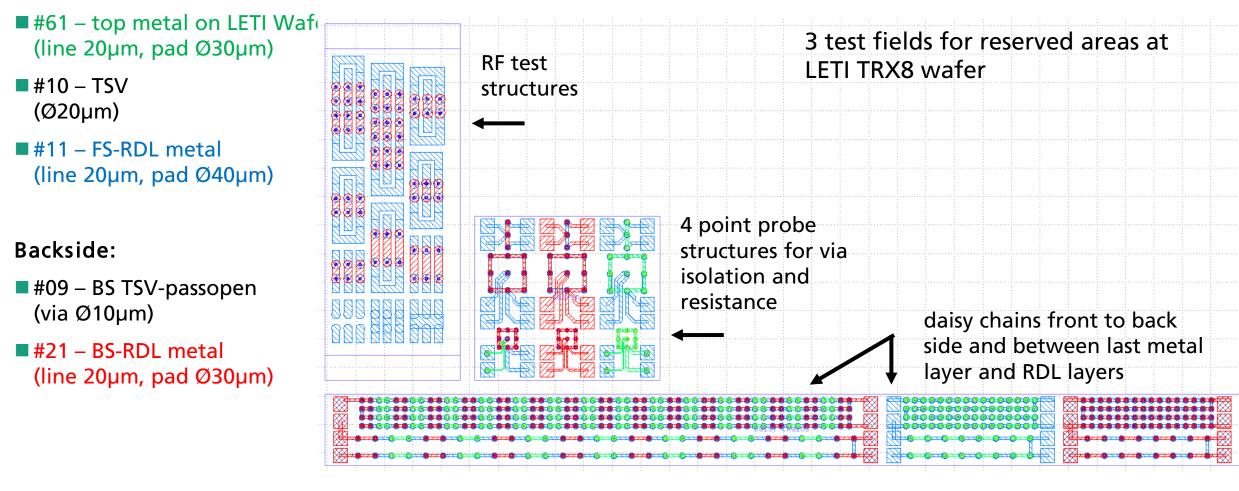

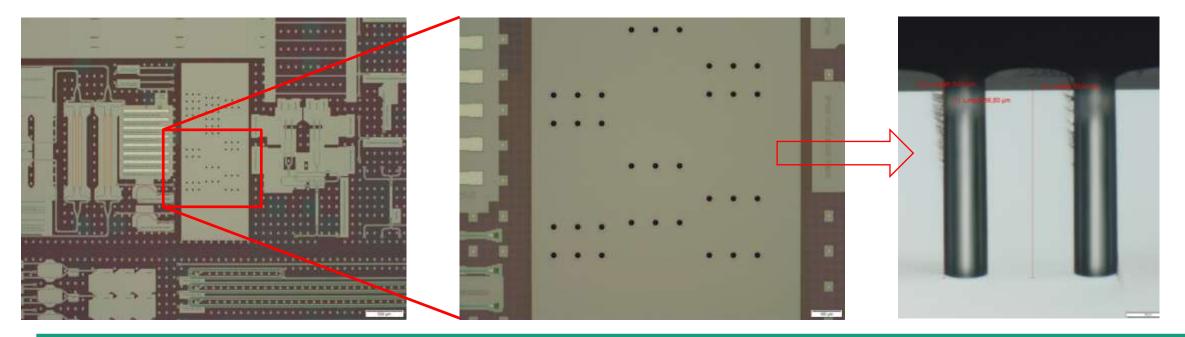

### Layers and Test Structures for TSV Characterization

#### Frontside:

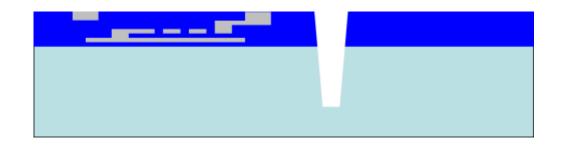

### Wafer after TSV blind hole etching and Cu filling

- Lithography and Alignment established  $\checkmark$

- BEOL etching established  $\checkmark$

- SI-DRIE etching established ✓

- CVD / PVD / Cu-Plating to be done

Co-funded by the Horizon 2020

Framework Programme of the European Union

MASSTART project is co-funded by the Horizon 2020 Framework Programme of the European Union with Grant Agreement Nr. 825109. <u>https://cordis.europa.eu/project/rcn/219912/factsheet/en</u>

MASSTART project is an initiative of the Photonics Public Private Partnership <u>www.photonics21.org</u>

Bogdan Sirbu, WLSI 18 Photonics Days Berlin Brandenburg, 05.10.2021 © Fraunhofer IZM